ТИМОШКИН А. И. – к.т.н. (Ростовская академия сервиса ЮРГУЭС)

## КОНТРОЛЕПРИГОДНАЯ СХЕМА ДВОИЧНОГО УМНОЖИТЕЛЯ ДЛЯ БАНКА ДАННЫХ САПР СБИС

Статью представил д.ф.-м.н., проф. Гаврилюк В. И.

Одним из эффективных подходов к проблеме проектирования контролепригодных цифровых систем на кристаллах (т.е. реализованных в виде отдельных БИС и СБИС) является подход, основанный на структурной композиции. Сущность этого подхода заключается в создании использовании в САПР СБИС иерархической системы библиотек (или банка данных) наиболее характерных для цифровых систем контролепригодных цифровых элементов, узлов и блоков [1]. Такой подход приводит к существенному сокращению сроков проектирования и повышению качества проектов контролепригодных цифровых систем на БИС и СБИС.

К наиболее характерным для современных цифровых систем (особенно для сигнальных и медийных) на БИС и СБИС функциональным блокам относятся, в частности, умножители различных типов [2]. В работе [3] предложена контролепригодная функциональнологическая схема однотактного матричного двоичного умножителя, обладающая проверяющим тестом длины 5 относительно ее одиночных константных неисправностей. В данной работе рассматривается контролепригодная схема однотактного матричного умножителя, обладающая проверяющим тестом длины относительно одиночных такой же константных неисправностей, но более быстродействующая и требующая для своей реализации меньшего объема аппаратных средств.

Основу предлагаемой схемы, как и схемы из работы [3], составляют слои одноразрядных сумматоров, объединенных в пределах каждого слоя в сумматор параллельного действия с последовательным переносом. При этом, в отличие от работ [3, 4], построение контролепригодной схемы одноразрядного сумматора каждого слоя, базируется на представлении функции суммы S не в форме по-

линомиальной суммы по модулю 2 (полинома Жегалкина), а в форме, двойственного полиному Жегалкина, или в форме полиномиальной суммы по эквивалентности (или эквиваленции, равнозначности):

$$S = a \circ b \circ p \tag{1}$$

где a и b — значения сигналов исходных одноразрядных операндов, p — значение входного сигнала переноса, S — значение сигнала суммы,  $\mathfrak d$  — символ эквивалентности. Функция же переноса P представляется в этом случае в форме, являющейся двойственной «смешанной» форме из работы [4]:

$$P = [(pva) \circ (pvb)] & (avb) =$$

$$[pv(a\circ b)] & (avb)$$

(2)

где p, P — значения входного и выходного сигналов переноса соответственно, v — символ дизъюнкции, & — символ конъюнкции. Такие представления функций суммы и переноса основаны на принципе двойственности [5] и справедливы, поскольку эти функции являются самодвойственными.

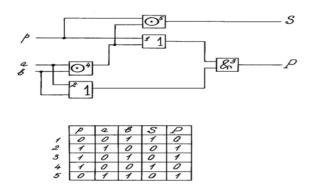

Контролепригодная логическая схема одноразрядного сумматора, реализованная по формулам (1) и (2), показана на рис. 1. Проверяющий тест для этой схемы относительно всех одиночных константных неисправностей содержит 5 векторов и описывается таблицей, представленной на рис. 1. Обнаружение отмеченных неисправностей этой схемы происходит следующим образом. Тестовые векторы 1,2, 4 и 5 из таблицы рис. 1 обнаруживает все одиночные константные неисправности данной схемы, кроме одиночной неисправности типа «константа 0» на том

входе дизъюнктора 2, который связан с внешним входом b. Эту неисправность обнаруживает тестовый вектор 3.

Рис.1. Контролепригодная схема одноразрядного сумматора

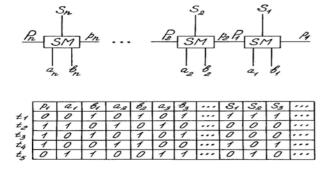

Контролепригодная схема n —разрядного (где n — натуральное число) двоичного сумматора каждого слоя рассматриваемого матричного умножителя получается из n контролепригодных схем полного одноразрядного сумматора обычным путем, т.е. соединением выхода переноса i-й схемы со входом переноса (i+1)-й схемы, где  $1 \le i \le n-1$ . Эта схема приведена на рис. 2.

Рис.2. Контролепригодная схема *п*-разрядного сумматора

Проверяющий тест T для контролепригодной схемы n-разрядного двоичного сумматора относительно всех ее одиночных константных неисправностей состоит из двух частей  $T = T_1 T_2$  и строится следующим образом:

— часть  $T_1$  содержит три тестовых вектора  $t_1$ ,  $t_2$ ,  $t_3$ , которые образуются путем простой итерации соответственно первого, вто-

рого и третьего тестовых векторов из таблицы рис. 1 для всех разрядов;

— часть  $T_2$  содержит два тестовых вектора  $t_4$ ,  $t_5$ . Тестовый вектор  $t_4$  образуется путем итерации четвертого тестового вектора из таблицы рис.1 для нечетных разрядов и пятого тестового вектора из этой таблицы для четных разрядов. Тестовый вектор  $t_5$ , наоборот, образуется путем итерации пятого тестового вектора из таблицы рис. 1 для нечетных разрядов и четвертого тестового вектора из этой таблицы для четных разрядов.

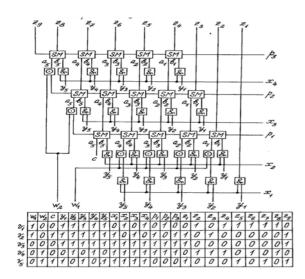

Тест T описывается таблицей, представленной на рис. 2. Контролепригодная функционально-логическая схема однотактного  $n \times m$ -разрядного матричного умножителя (где n — число разрядов множимого, m — число разрядов множителя) для случая n = 5, m = 4 приведена на рис. 3. Эта схема, как и схема обычного  $5 \times 4$  —разрядного матричного умножителя, содержит три слоя сумматоров и четыре слоя конъюкторов. Однако, как уже отмечалось, схемы сумматоров реализованы по приведенным выше формулам.

Помимо этого, рассматриваемая схема содержит шесть дополнительных двухвходовых элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ» (равнозначность) и два дополнительных входа  $W_1$ ,  $W_2$ . При этом в рабочем режиме на входы c,  $p_1$ ,  $p_2$ ,  $p_3$  попадаются сигналы логического «0», а на входы  $W_1$ ,  $W_2$  — сигналы логической «1». Проверяющий тест для этой схемы относительно всех ее одиночных константных неисправностей содержит 5 векторов и описывается таблицей рис. 3.

При подаче на выходы схемы тестовых векторов из таблицы (см. рис. 3) в последовательности  $V_1$ ,  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$  на входы сумматора первого слоя поступят тестовые векторы из таблицы рис. 2 в последовательности  $t_1$ ,  $t_2$ ,  $t_3$ ,  $t_4$ ,  $t_5$ ; на входы сумматора второго слоя — тестовые векторы из таблицы рис. 2 в последовательности  $t_2$ ,  $t_1$ ,  $t_3$ ,  $t_4$ ,  $t_5$ ; на входы сумматора третьего слоя — тестовые векторы

из таблицы рис. 2 в последовательности  $t_1$ ,  $t_2$ ,  $t_3$ ,  $t_4$ ,  $t_5$ , т. е. обеспечивается подача на входы n-разрядного сумматора каждого слоя проверяющего теста этого сумматора относительно одиночных константных неисправностей. При этом также обеспечивается подача на входы каждого слоя коньюкторов их проверяющих тестов и подача на входы дополнительных элементов «исключающее ИЛИ-НЕ» (равнозначность) проверяющих тестов этих элементов.

Рис.3. Контролепригодная схема 5×4матричного умножителя

Легко видеть, что в общем случае, т. е. когда п и m — произвольные натуральные числа, контролепригодная функциональнологическая схема однотактного матричного умножителя содержит m-1 сумматоров с последовательным переносом, m слоев конъюнкторов, а также n+m-3 дополнительных элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ». Число дополнительных входов при этом не изменится и останется равным двум.

Проверяющий лист тест для общего случая также содержит 5 векторов и строится следующим образом:

- на каждый вход  $y_j$  подается последовательность 1, 1, 1, 0, если j нечетное число, и последовательность 1, 1, 1, 1, 0, если j четное число (j  $\varepsilon$  {1, 2,...., n});

- на каждый вход  $x_1$  подается последовательность 0, 1, 1, 1, 1, если i нечетное

число, и последовательность 1, 0, 1, 1, 1, если i – четное число (i  $\in$  {1, 2, ..., m});

- на каждый вход  $p_k$  подается последовательность 0, 1, 1, 1, 0, если k нечетное число, и последовательность 1, 0, 1, 1, 0, если k четное число (k  $\epsilon$  {1, 2, ..., m 1});

- на вход  $W_1$  подается последовательность 1, 1, 0, 0, 0, а вход  $W_2$  последовательность 0, 0, 0, 0, 1, 1;

- на вход c подается последовательность 0, 1, 0, 0, 1, если n нечетное число, и последовательность 0, 1, 0, 1, 0, если n четное число.

Схема одноразрядного сумматора, лежащая в основе рассматриваемой контролепригодной схемы матричного двоичного умножителя, легко преобразуется в схему, отличающуюся от схемы на рис. 1 только тем, что логические элементы 1, 2, 3 последней заменены логическими элементами «ИЛИ-НЕ». Проверяющий тест контролепригодной схемы матричного двоичного умножителя, которая получается в результате данного преобразования схемы одноразрядного сумматора, останется прежним. При этом полученная контролепригодная схема в случае реализации ее на основе МОП-технологии потребует значительно меньших аппаратных затрат, чем рассмотренная ранее в работе [3] контролепригодная схема. Это возможно благодаря тому, что известна очень простая реализация элемента «равнозначность» на основе технологии [6] (требуется всего 3 транзистора!). Кроме того, предлагаемая схема обладает более высоким быстродействием по сравнению с более ранней [3], поскольку с основе ее многоразрядных сумматоров лежит более быстродействующий однозарядный сумматор.

## Библиографический список

1. Интеллектуальные системы автоматизированного проектирования больших и сверхбольших интегральных микросхем [Текст] / под ред. В. А. Мищенко. – М.: Радио и связь, 1988. – 365 с.

- 2. Корнеев, В. В. Современные микропроцессоры [Текст] / В. В. Корнеев, А. В. Киселев. СПб.: БХВ Петербург, 2003. 277 с.

- 3. Тимошкин, А. И. Контролепригодная схема матричного двоичного умножителя [Текст] / А. И. Тимошкин // Электроника: НТБ. 2004. –№4. –С. 56-57.

- 4. Тимошкин, А. И. Контролепригодные схемы двоичных сумматоров для банка САПР СБИС. [Текст] / А. И. Тимошкин // Научная мысль Кавказа. Предложение. 2004. №4. —С. 124-129.

- 5. Яблонский, С. В. Введение в дискретную математику [Текст] / С. В. Яблонский. М.: Наука, 1986. 452 с.

- 6. Мурога, С. Системное проектирование сверхбольших интегральных схем [Текст] / С. Мурога. М.: Мир, 1985. 326 с.

**Ключевые слова:** контролепригодная схема, матричный двоичный умножитель, логическими элементами.

**Ключові слова:** контролепридатна схема, матричний двійковий множник, логічний елемент.

**Key words:** testable scheme, matrix binary multipleir, logical elements.

Надійшла до редколегії 7.07.2011. Прийнята до друку 8.07.2011.